# First Set of OS Architecture Models

**Project Deliverable D5.3 v1.0**

Tommaso Cucinotta, Giuseppe Lipari (SSSA)

Rui Aguiar, João Paulo Barraca, Bruno Santos and Javad Zarrin (IT)

Jan Kuper and Christiaan Baaij (UT)

Lutz Schubert and Daniel Rubio Bonilla (USTUTT-HLRS)

Vincent Gramoli (EPFL)

Due date: 31/07/2011 Delivery date: 21/08/2011

This work is partially funded by the European Commission under FP7-ICT-2009.8.1, GA no. 248465

(c) 2010-2012 by the S(o)OS consortium

This work is licensed under the Creative Commons Attribution 3.0 License.

To view a copy of this license, visit http://creativecommons.org/licenses/by/3.0/ or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

# **Version History**

| Version | Date     | Change                                                                                  | Author                                |

|---------|----------|-----------------------------------------------------------------------------------------|---------------------------------------|

| 0.1     | 24/05/11 | First TOC                                                                               | Tommaso Cucinotta                     |

| 0.2     | 02/06/11 | Second TOC and preliminary contributions                                                | Tommaso Cucinotta, all                |

| 0.3     | 08/06/11 | Refined TOC and contributions re-arrangement                                            | Tommaso Cucinotta                     |

| 0.4     | 10/06/11 | Merged HLRS contributions                                                               | Tommaso Cucinotta,<br>Lutz Schubert   |

| 0.5     | 17/06/11 | Merged refined contributions and partial TOC rearrangement.                             | Tommaso Cucinotta, all                |

| 0.6     | 22/06/11 | Merged chapters restructuring by HLRS                                                   | Lutz Schubert                         |

| 0.7     | 24/06/11 | Merged EPFL & SSSA contributions                                                        | Tommaso Cucinotta,<br>Vincent Gramoli |

| 0.8     | 30/06/11 | Merged OS Requirements Tables                                                           | Tommaso Cucinotta, all                |

| 0.9     | 01/07/11 | OS Requirements fixup                                                                   | Tommaso Cucinotta, all                |

| 0.10    | 04/07/11 | Clarified meaning of OS Requirements                                                    | Tommaso Cucinotta                     |

| 0.11    | 07/07/11 | Merged dependencies summary and various restructuring of sections                       | Tommaso Cucinotta, all                |

| 0.12    | 02/07/11 | Further restructuring; extended dependencies table; added overarching architecture view | Lutz Schubert, all                    |

| 0.13    | 18/07/11 | Refined code analysis section                                                           | Lutz Schubert                         |

| 0.14    | 28/07/11 | Added scenario & requirements restrictions                                              | Lutz Schubert                         |

| 0.15    | 02/08/11 | Extended architecture integration section; integrated various extensions                | Lutz Schubert, all                    |

| 0.16    | 09/08/11 | Extended API discussion                                                                 | Lutz Schubert                         |

| 0.17    | 21/08/11 | Various fix-ups, addressing final comments & typos                                      | Tommaso Cucinotta,<br>Lutz Schubert   |

| 0.18    | 21/08/11 | Final fix-ups, proof-reading, typos, punctuation, bibliography fixes.                   | Tommaso Cucinotta                     |

| 0.19    | 22/08/11 | Last-mile fixes by EPFL & SSSA                                                          | Tommaso Cucinotta                     |

| 1.0     | 23/08/11 | Final version ready for submission to the EC                                            | Lutz Schubert                         |

## **EXECUTIVE SUMMARY**

This document reports the results of the preliminary investigations about general Operating System (OS) architecture models that will make it easier for developers to code applications on massively parallel and distributed systems as expected to be available in 10-15 years in the future. The discussion focuses first on a small set of target application scenarios which are useful to highlight particularly critical requirements posed by the applications on the OS, as arising in the context of S(o)OS. These requirements are mainly related to scalability issues of nowadays OSes and run-time environments. Then, the OS architecture model is sketched out in terms of subcomponents, their interconnections and interdependencies and behaviour. However, as this constitutes a first preliminary investigation that will be refined in the future version of this deliverable D5.4, the whole set of details of an OS architecture are not deeply discussed, but rather the focus is on those aspects that are critical for the project objectives. A recurring discussion in this context relates to kernelversus user-space location of the OS/kernel components, which we however want to avoid in this first iteration, for the sake of concentrating on the OS capabilities in the first instance. Indeed, the definition of a whole OS architecture is actually outside the scope of the S(o)OS project. The main focus of this document (and of the refined version that will be released later) is the one to identify critical architectural elements and subcomponents that, constituting major bottlenecks in nowadays operating systems, need to be reviewed and rethought for the purpose of being able to face with future massively parallel and distributed systems so as to expose the available computing power to a broad range of developers, ranging from average developers to highly experienced ones.

# **TABLE OF CONTENTS**

| EXECUT     | IVE SUMMARY                                | 4  |

|------------|--------------------------------------------|----|

| TABLE O    | OF CONTENTS                                | 6  |

| LIST OF    | FIGURES                                    | 9  |

| LIST OF    | TABLES                                     | 10 |

| ABBREV     | /IATIONS                                   | 11 |

| TERMS      |                                            | 12 |

| I. INTRO   | DUCTION                                    | 13 |

|            | 1. Organisation of this document           | 13 |

| II. S(O)O  | OS BASIC CONCEPTS                          | 14 |

|            | 1. HARDWARE TRENDS                         | 14 |

|            | 1.a) Abstracting the Hardware              | 15 |

|            | 1.B) S(O)OS INFRASTRUCTURE CHARACTERISTICS | 17 |

|            | 2. THE ROLE OF THE OS                      | 18 |

|            | 3. MAIN S(O)OS PRINCIPLES                  | 19 |

|            | 4. Application Behaviour                   | 20 |

|            | 5. S(o)OS APPLICATION LIFE CYCLE           | 22 |

|            | 5.a) Development                           | 23 |

|            | 5.b) Compilation                           | 23 |

|            | 5.c) Code Analysis                         | 24 |

|            | 5.d) Resource Identification               | 25 |

|            | 5.e) Execution Preparation                 |    |

|            | 5.f) DISTRIBUTED EXECUTION                 | 27 |

|            | 5.g) Post Processing                       | 28 |

| III. USE ( | CASES AND REQUIREMENTS                     | 29 |

|            | 1. Specific Use Cases                      | 29 |

|            | 1.a) Scalable HPC Application              | 29 |

|            | 1.b) SCALABLE DISTRIBUTED RT APPLICATION   | 32 |

|            | 2. HIGH-LEVEL OS REQUIREMENTS              | 33 |

|            | 2.A) DISCUSSION                            | 37 |

|            | 2.b) Prioritisation of the OS Requirements | 41 |

|            | 2.c) Low-level Requirements on the OS      | 41 |

|            |                                            |    |

| IV. O | S ARCHITECTURE MODELS                         | 44 |

|-------|-----------------------------------------------|----|

|       | 1. Background                                 | 44 |

|       | 1.A) CURRENT OS ARCHITECTURE CONCEPTS         | 44 |

|       | 1.B) GENERAL CONCEPTS                         | 45 |

|       | 2. S(o)OS ARCHITECTURE CONCEPTS               | 47 |

|       | 2.a) General S(o)OS Architecture              | 47 |

|       | 2.B) S(O)OS LAYOUT CONCEPTS                   | 50 |

| V. CR | RITICAL OS CAPABILITIES                       | 56 |

|       | 1. CODE ANALYSIS AND SEGMENTATION             | 56 |

|       | 1.a) Code Behaviour Analysis & Monitoring     | 57 |

|       | 1.B) CODE TRANSFORMATION AND ADAPTATION       | 59 |

|       | 1.c) External Requirements and Dependencies   | 60 |

|       | 1.d) Architecture Sketch                      | 62 |

|       | 2. BINARY CODE ADAPTATION                     | 62 |

|       | 2.a) Motivation                               | 62 |

|       | 2.B) SET OF FUNCTIONALITY THE OS MUST PROVIDE | 63 |

|       | 2.c) Optional Extension                       | 64 |

|       | 2.d) Code Development                         | 65 |

|       | 2.E) Interaction with other OS modules        | 65 |

|       | 3. RESOURCE DESCRIPTION                       |    |

|       | 3.A) MOTIVATION                               |    |

|       | 3.B) MINIMALLY REQUIRED OS FUNCTIONALITY      |    |

|       | 3.c) Optional OS Functionality                |    |

|       | 3.d) Implications of use-case scenarios       |    |

|       | 3.e) HIERARCHICAL RESOURCE DESCRIPTION        |    |

|       | 4. RESOURCE DISCOVERY AND MATCHING            |    |

|       | 4.A) RESOURCE DISCOVERY                       |    |

|       | 4.b) Required OS Components                   |    |

|       | 4.c) IMPACT ON OTHER OS COMPONENTS            |    |

|       | 5. Scheduling                                 |    |

|       | 5.a) Performance prediction                   |    |

|       | 5.B) EXECUTION TIMES ON TILE-BASED SYSTEMS    |    |

|       | 5.c) Deploying Tasks in Tile-based Systems    |    |

|       | 5.d) Code Distribution Costs and Criteria     |    |

|       | 5.e) REQUIRED OS COMPONENTS                   |    |

|       | 6. In-chip Communications                     |    |

|       | 7. COMPONENT-BASED ASYNCHRONOUS KERNEL        |    |

|       | 7.A) MOTIVATION                               |    |

|       | 7.B) REQUIRED OS COMPONENTS                   |    |

|       | 7.c) IMPACT ON OTHER OS COMPONENTS            |    |

|       | 8. Transactional Memory                       |    |

|       | 8.A) KERNEL-LEVEL TRANSACTIONS                |    |

|       | 8.b) Modularity in Locking Schemes            | 88 |

| 8.c) File System Use-Case: I/O and Syscalls Problems and Solutions | 88  |

|--------------------------------------------------------------------|-----|

| 8.d) Application Use-Case: Real-time Streaming application         | 89  |

| 8.e) Relations with Other Components                               | 89  |

| 9. Speculative Execution                                           | 90  |

| 9.a) Motivation                                                    | 90  |

| 9.B) MINIMUM SET OF FUNCTIONALITY THE OS MUST PROVIDE              | 90  |

| 9.c) Optional Extension                                            | 91  |

| 9.d) Automatic SAM                                                 | 93  |

| 9.e) Code Development                                              | 93  |

| 9.f) Interaction with other OS modules                             | 93  |

| 9.g) SAM HARDWARE SUPPORT ASSISTED BY THE OS                       | 94  |

| VI. OS ARCHITECTURE                                                | 95  |

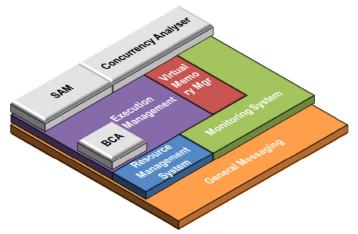

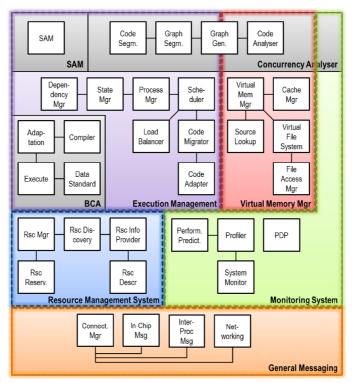

| 1. OS Functionality Sets                                           | 95  |

| 1.A) BASE OS CAPABILITY SETS                                       | 96  |

| 1.B) MAIN OS CAPABILITY SETS                                       | 97  |

| 1.c) OS Supporting Capability Sets                                 | 100 |

| 2. OS COMPONENTS RELATIONSHIPS                                     | 102 |

| 2.a) Summary of Dependencies                                       | 103 |

| VII. APPLICATION PROGRAMMING INTERFACE                             | 104 |

| 1. PARALLELISM AND CONCURRENCY                                     | 104 |

| 1.A) INTERPRETING DATA SPECIFIC BEHAVIOUR                          | 104 |

| 1.B) IDENTIFYING CODE-DATA-RELATIONSHIPS                           | 105 |

| 1.c) Resource Type Helpers                                         | 106 |

| 2. REAL-TIME PROGRAMMING                                           | 106 |

| 3. Transactional Memory Interface                                  | 107 |

| 3.A) TM COMPREHENSIVE INTERFACE                                    | 107 |

| 3.B) TM REDUCED INTERFACE                                          | 108 |

| 3.c) Contention Manager Interface                                  | 109 |

| VIII. CONCLUSIONS AND FUTURE WORK                                  | 110 |

| 1. GENERAL FUTURE WORK                                             | 110 |

| 2. COMPONENTS RELATED FUTURE WORK                                  | 110 |

| REFERENCES                                                         | 114 |

# **LIST OF FIGURES**

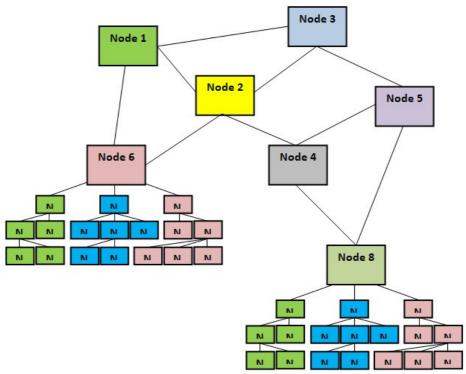

| Figure 1: "new" von Neumann architecture                                                                       | 15        |

|----------------------------------------------------------------------------------------------------------------|-----------|

| Figure 2: Flat description of a hardware architecture                                                          | 16        |

| FIGURE 3: S(0)OS' EXTENDED APPLICATION LIFECYCLE                                                               | 22        |

| Figure 4: Basic blocks in an assembly code snippet and associated control graph                                | 25        |

| Figure 5: Layouting the code according to the infrastructure specifics                                         | 25        |

| Figure 6:Different code segmentations and the impact on communication                                          | 26        |

| Figure 7: Deploying code segments in according resources                                                       | 27        |

| FIGURE 8: MEMORY ALLOCATION OF CODE SEGMENTS, SHARE DATA AND OS SERVICES                                       | 27        |

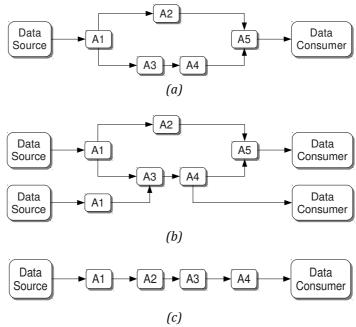

| Figure 9: Real-Time Application composed of a DAG (a) with possibly multiple data sources and consumers (b)    | , OR THE  |

| SIMPLE CASE OF A LINEAR WORKFLOW OF ACTIVITIES (C)                                                             | 32        |

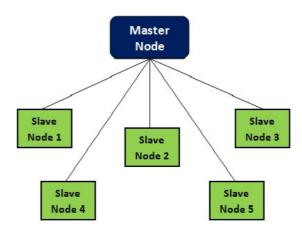

| Figure 10: Centralised deployment                                                                              | 51        |

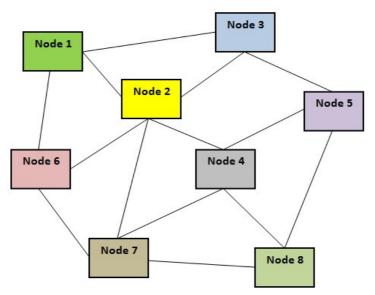

| Figure 11: Fully distributed architecture                                                                      | 51        |

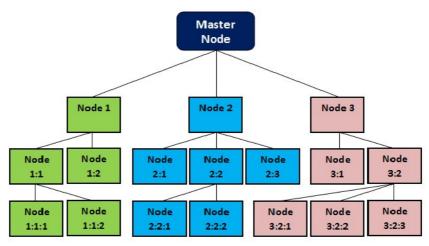

| FIGURE 12: ARCHITECTURE OF A HIERARCHICAL CENTRALISED DEPLOYMENT                                               | 52        |

| Figure 13: Distributed Hierarchical communication architecture                                                 | 52        |

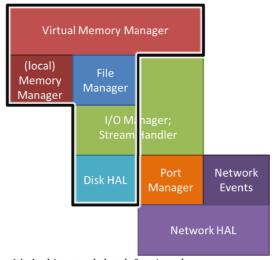

| FIGURE 14: ARCHITECTURAL SKETCH FOR VIRTUAL MEMORY MANAGEMENT                                                  | 54        |

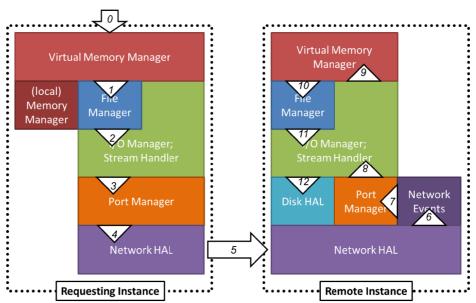

| FIGURE 15: ROUTING A REQUEST OVER INSTANCES AND MODULES - THE NUMBERS DENOTE THE SEQUENCE OF STEPS             | 55        |

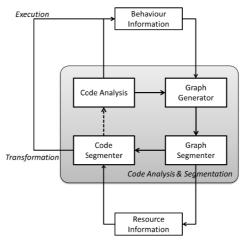

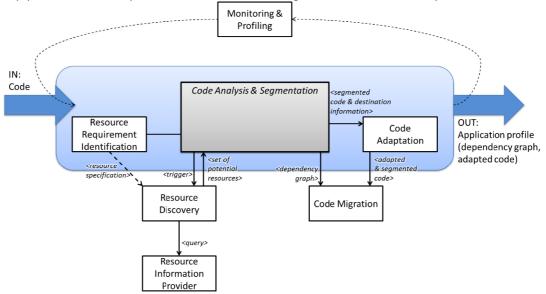

| Figure 16: General architecture principles of code analysis & segmentation                                     | 57        |

| Figure 17: Conceptual behaviour of the code analysis & segmentation related components (and their dependent    | CIES). 62 |

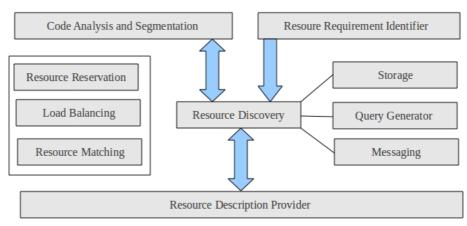

| FIGURE 18: INTERACTION OF RESOURCE DISCOVERY WITH OTHER OS COMPONENTS                                          | 72        |

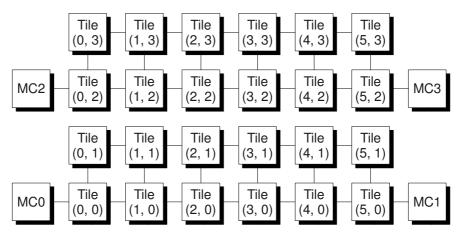

| Figure 19: Layout of the 24-tiles mesh network within the Intel SCC chip. Cores have IDs increasing along the  | HE X TILE |

| COORDINATE, THEN THE Y COORDINATE, E.G., TILE (0, 0) INCLUDES CORES 0 AND 1, TILE (5, 0) CORES 10 AND 11 AND   | TILE (5,  |

| 3) INCLUDES CORES 46 AND 47                                                                                    | 75        |

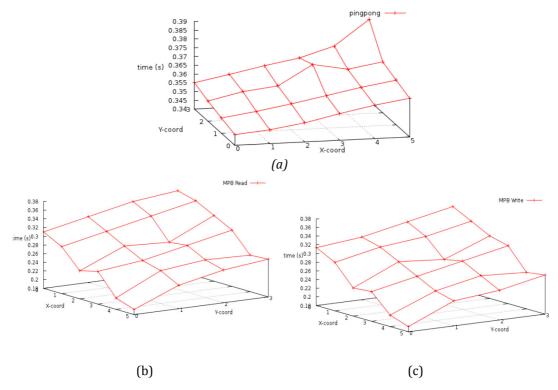

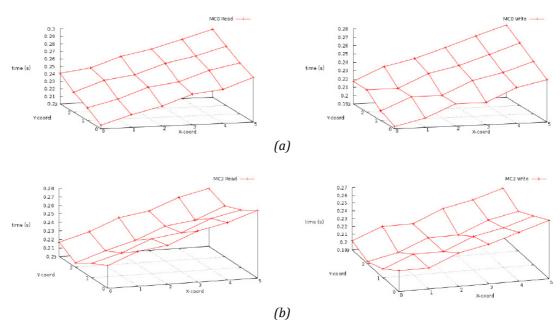

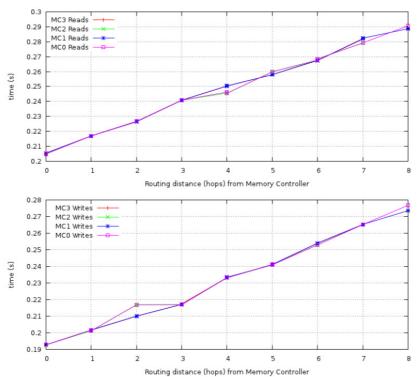

| Figure 20: Times for: (a) round-trip message-passing between the first core and each other core; (b) read tim  | ES FROM   |

| CORE 11 TO EACH OTHER CORE'S MPB BUFFER; (C) WRITE TIMES FROM CORE 11 TO EACH OTHER CORE'S MPB BUFFER          | 76        |

| Figure 21: Times for reading (left pictures) and writing (right pictures) 1MB from/to the off-chip memory fro  | OM EACH   |

| CORE (COORDINATES ON X AND Y AXES), WHEN THE MEMORY PAGES ARE ALLOCATED IN THE FIRST (A) AND THIRD (B)         | MEMORY    |

| CONTROLLERS                                                                                                    | 77        |

| Figure 22: Read (top) and write (bottom) times as a function of the routing distance between each core         | AND THE   |

| TARGET MEMORY CONTROLLER                                                                                       | 77        |

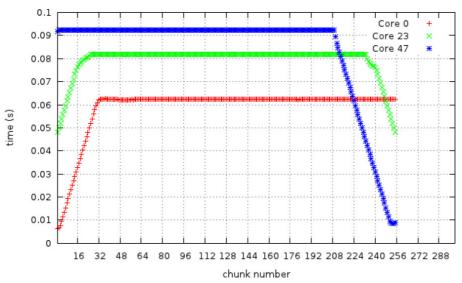

| Figure 23: Execution times in the first, 23rd and 47th stages of the pipeline, as experienced on the various   | CHUNKS    |

| PROCESSED THROUGH THE PIPELINE, IN THE UNCACHED SHARED MEMORY CASE                                             | 78        |

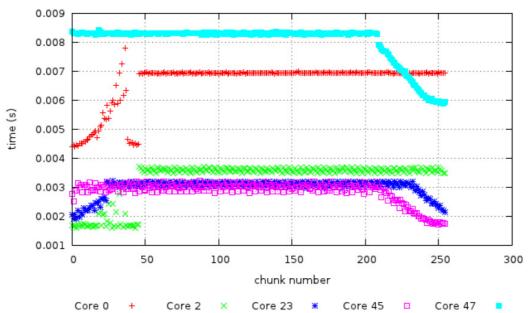

| Figure 24: Execution times in various stages of the pipeline, as experienced on the various chunks processed t | HROUGH    |

| THE PIPELINE, IN THE CACHED SHARED MEMORY CASE. CORES 0 AND 47 SHOW GENERALLY HIGHER TIMES SINCE THE           | SE CORES  |

| ADDITIONALLY HAVE THE TASK OF READING DATA FROM INPUT BUFFERS INTO THE PIPELINE AND OF WRITING DATA FR         | ROM THE   |

| PIPELINE INTO THE OUTPUT BUFFER                                                                                | 79        |

| Figure 25: Basic dependency architecture model                                                                 | 96        |

| Figure 26: OS dependency architecture                                                                          | 102       |

# **LIST OF TABLES**

| Table 1: Prioritisation of high-level OS requirements          | 41  |

|----------------------------------------------------------------|-----|

| Table 2: Relationship between low- and high-level requirements | 43  |

| TABLE 3. DEDENDENCIES OVERVIEW OVER THE COMPONENTS             | 103 |

# **ABBREVIATIONS**

| Abbreviation | Description                                  |

|--------------|----------------------------------------------|

| ABI          | Application Binary Interface                 |

| API          | Application-Programming Interface            |

| ccNUMA       | Cache Coherent NUMA                          |

| CPU          | Central Processing Unit                      |

| FS           | File System                                  |

| GPU          | Graphics Processing Unit                     |

| GPGPU        | General-Purpose GPU                          |

| HTM          | Hardware-based Transactional Memory          |

| IPP          | Integrated Performance Primitives (by Intel) |

| ISA          | Instruction-Set Architecture                 |

| MPI          | Message-Passing Interface                    |

| NoC          | Network-on-a-Chip                            |

| NUMA         | Non-Uniform Memory Architecture              |

| OS           | Operating System                             |

| PGAS         | Partitioned Global Address Space             |

| QoS          | Quality of Service                           |

| RD           | Resource Discovery                           |

| S(o)OS       | Service-oriented Operating Systems           |

| SCC          | Single-chip Cloud Computer (by Intel)        |

| SSI          | Single-System Image                          |

| STM          | Software Transactional Memory                |

| TM           | Transactional Memory                         |

# **TERMS**

| Term                | Definition                                                               |

|---------------------|--------------------------------------------------------------------------|

| Kernel              | Core part of an OS implementing basic fundamental functionality that     |

|                     | serve as a basis for realising all of the other OS services.             |

| Node, Machine, Host | All synonyms denoting a physically separated autonomous computing        |

|                     | element (a PC, a node inside an HPC rack, etc.), which is connected to   |

|                     | other elements via network adapters.                                     |

| Thread              | Single thread of execution, sharing the same memory space as all the     |

|                     | other threads belonging to the same process.                             |

| Process             | A process is composed of one or more threads. Processes on the same OS   |

|                     | do not share the same memory space, however they can use shared          |

|                     | memory segments if they use explicitly the corresponding OS services.    |

| Task                | Synonym of thread.                                                       |

| Code Segment        | A piece of a program that can be extracted from a process, and executed  |

|                     | on a different core than the one where the rest of the process is being  |

|                     | executed. For example, a sequential execution involving a loop over a    |

|                     | large number of items can be split into code segments to be executed on  |

|                     | different cores in parallel for enhanced performance.                    |

| Scheduling          | The algorithm by which it is decided which physical resources are        |

|                     | allocated to which program execution units and when. For example,        |

|                     | scheduling code segments, threads and processes over the available       |

|                     | cores and processors, scheduling the network packets over the available  |

|                     | network adapters, etc.                                                   |

| Scalability         | Property of a system to not suffer of major performance penalties as its |

|                     | size grows.                                                              |

| Component,          | An OS component, or OS module, or OS Service, is a piece of software     |

| Module, Service     | implementing a specific OS functionality.                                |

| Driver              | A specific component of an OS supporting a specific hardware capability, |

|                     | peripheral or peripheral type.                                           |

| Operating System    | The run-time environment that mediates the interactions between an       |

|                     | application and the underlying hardware, simplifying the task of writing |

|                     | applications for a variety of physical platforms.                        |

| Middleware          | Software layer mediating the interactions between the applications and   |

|                     | the core part of an OS. An OS itself may include middleware components   |

|                     | for the purpose of providing application developers with high-level and  |

|                     | powerful management interfaces.                                          |

| Service, Primitive  | OS functionality or OS component(s) implementing a particular            |

|                     | functionality.                                                           |

### I. Introduction

With the movement from single-core machines to large-scale heterogeneous multi- and many-core processors, the classical development and even execution paradigms changed completely: not only does the average developer has to face challenges similar to the ones in the HPC domain, but also HPC developers have to cater for a much more complex environment, requiring even higher expertise than before. Whilst the general tendency seems to consist in shifting the burden to the developer, the S(o)OS project aims at significantly reducing this burden through increased support by the operating system.

This means in particular that the OS must provide a method to abstract the underlying hardware and enable a common execution model on top of it, yet still be able to exploit the respective capabilities in the best fashion for the program. At the same time, it must be enabled to deal with the large amount of resources, at least without affecting negatively the performance of the deployed applications. Current operating systems fail with both of these respects.

### 1. ORGANISATION OF THIS DOCUMENT

This document is organised as follows.

In Chapter II., basic concepts around the need for designing novel operating systems are shortly recalled, starting from summarising key hardware characteristics that future massively parallel systems will posses, and proceedings to highlight the shortcomings of nowadays OSes as well as the potential for overcoming them in a novel S(o)OS operating system. We outline how we foresee S(o)OS to behave in the context of a generic application lifecycle, thereby highlighting the main benefits and challenges.

In Chapter III., we list the general OS requirements which are critical for the project, and whose importance is highlighted by focusing on a couple of application scenarios particularly critical for the project. These help in shaping the requirements towards a next-generation class of OSes which are able to overcome such limitations.

In Chapter IV., we depict a preliminary set of OS architecture models, detailing what are the set of possible OS components, services and functionality and what is their layout in terms of distribution and interactions across a massively parallel physical system.

In Chapter V. , we focus on a subset of OS services which are particularly critical in the context of many-core and massively parallel systems. These include resource discovery and matching, including the support for heterogeneous hardware, scheduling, and others.

In Chapter VI, we discuss the relationships and interactions between these services, thus developing the integrative view on the S(o)OS architecture. We thereby classify the components and align them to the general architecture discussions in chapter IV.

In Chapter VII., we provide a preliminary discussion on issues specifically related to the API and the programmability of applications in the context of an OS with the enriched functionality and the architecture model as described in the previous chapters.

Finally, conclusions and the research roadmap for the following S(o)OS activities are sketched out in Chapter VIII.

# II. S(0)OS BASIC CONCEPTS

In this chapter we overview the key concepts at the basis of a novel operating system architecture for massively parallel and distributed systems. This is done by recalling first what are the hardware trends that massively parallel systems will see in the future, then summarising the shortcomings of nowadays OSes and key innovations that allow S(o)OS to overcome them.

#### 1. HARDWARE TRENDS

As detailed in the S(o)OS Deliverable D5.2 "Future Requirements" [15], a key characteristic of future many-core platforms consists in the increasing heterogeneity of the runtime environments, which will not only incorporate a large set of completely different resources, but, what is more, will differ strongly from one another. In other words, it must be expected that no two computing infrastructures will be the same in the future. Also, it must be generally assumed that the current development trends in processor and system manufacturing will continue and even grow in complexity. It is in particular notable that the era of the so-called "frequency race" has come to an end. This implies that future processor generations will no longer be faster (in terms of clock speed), but integrate more processing units instead, i.e. they will process more operations at the same time. Due to the nature of this form of processing, the classical (sequential) programming paradigm does not apply any more, and future code needs to be parallelised in order to still gain in performance. As manufacturers compete with each other to realise large scaling processors with high theoretical peak performance, this development has become known as the "core race".

However, it cannot be expected that all code is parallelised optimally – instead, many algorithms are essentially sequential in nature, or at least in parts (see [45]). Since the executing frequency can no longer be improved, manufacturers therefore try to develop specialised processing units that are explicitly built to perform specific actions well. Mathematical coprocessors and graphical processing units are historical examples of such specialised processors, that became very well known.

Modern processors already combine multiple specialised units, such as floating point, vector and general purpose units. In order to make best use of these resources, the developer has to organise the code accordingly, respectively adjust the algorithms to meet the hardware specifics. Not only does this imply additional effort for the developer, it also implies that portability of code becomes more and more problematic, as individual processors incorporate different specialised units.

Since there are no clear indicators either for the software requirements or the usage of future processors, nor for the optimal combination of specialised and general-purpose units under these circumstances, future processor generations will essentially be "experimental" in nature. In other words, manufacturers will take different approaches to iteratively improve the quality / performance of their processors. At the same time, the diversity of use cases, such as mobile, office, home and high performance computing, leads to a wide range of requirements that different manufacturers approach differently. To the normal divergence on grounds of lacking knowledge comes thus the divergence due to the variety of use cases.

Currently, there are processors emerging that incorporate fast and energy-saving cores allowing the system to switch between "performance" and "energy-saving" modes by switching between either core type, depending on workload and circumstances. On the other end of the spectrum, Intel is examining how to incorporate multiple homogeneous cores in a cloud like fashion on a single chip, whilst AMD is investigating a more hierarchical approach where segments share specialised floating point units. For more details, please refer to S(o)OS Deliverable D5.2 "Future Requirements" [15].

#### 1.A) ABSTRACTING THE HARDWARE

The divergence of application domains, and implicitly of hardware types, causes multiple problems not only on the program development side, but also on the operating system, as we will elaborate in more detail in the next section. In order to optimally deal with resource types, all details of the respective resource(s) should be known to the compiler / operating system / middleware. However, neither do manufacturers want to publish all this information, nor is the impact of these details onto code execution, let alone programming, fully understood. Efficient programming is typically mostly constrained by this lack of knowledge regarding the resource details.

What is more, these details would further restrict the portability of the code. Accordingly, it is neither feasible, nor sensible to act upon the whole resource details. Instead, ideally an abstraction level can be found that not only provides enough details for essential adaptation steps, but that also covers future developments to a wide degree, so that no constant re-adaptations of this information schema is needed.

From the most generic level of both optimisation and description, we can distinguish between essential resource "classes" along the lines of 1:

- memory/storage units;

- · processing units;

- · connection elements.

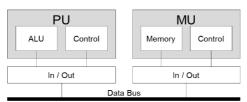

Each of these elements in turn have further characteristics that specify the concrete behaviour and low-level optimisation details – however, on the highest abstraction level, these three classes suffice to provide essential information about the potential degree of parallelisation, the distribution and adaptation of threads / processes and the communication impact. It will be noted that this description is closely related to von Neumann's architecture, which forms the basis of all modern processor architectures. Von Neumann's model is however insufficient to capture different levels of hierarchical storage over different communication layers, as well as multi-core units within a single processor. We therefore build upon a "new" von Neumann architecture as depicted in Figure 1, where multiple generic Processing Units (PU) and multiple generic Memory Units (MU) are

Figure 1: "new" von Neumann architecture

interconnected through proper interconnection elements (Data Bus in the picture).

This architecture allows us to equally cover local cache, as well as even Internet-provided storage, and single-core desktop machines, as well as large-scale cluster machines etc. Even though S(o)OS does not try to address all these varieties in the same degree, the principles of S(o)OS can thus be extended to cover further architectures, such as cloud infrastructures, or even future processor architectures. We claim thereby that developments such as 3d stacked memory are implicitly covered by this structure, too: any of these architectural choices will either be hidden to the developer, such as using shadow caches, in which case they subsume under the specific characteristics of a unit in the new von Neumann architecture, reflecting the special functionalities aimed at their respective development in the first instance. Or the choices will be explicitly exposed to the developer, in which case the respective choices are simple units in the new von Neumann architecture.

Note that we focus exclusively on hardware elements that are needed to support computing. For example, these classes do not cover peripherals.

According to this architecture, all units are connected via some form of communication link. In other words, processing units and memory (such as cache) are not connected directly, but via an interconnect that exhibits all the characteristics of a regular messaging route, i.e. are subject to latency and bandwidth restrictions. The model allows for multiple units of different type to be connected along the same communication link, or hierarchically using multiple routes with different connectivity and properties. It is secondary for this model that external devices (sensors, displays etc.) are equally connected via such a communication interconnect.

The model does not prescribe the type of either processing or memory unit – that is, they can equally well cover concrete low-level units, such as L1 cache and processing cores, as well as more abstract units, such as virtual files, internet-provided disks, tables, many-core processors, virtual hosts etc. In general, a processing unit is any entity that can execute computational tasks on data, and likewise a memory unit is any resource that can store data. It thereby does not matter whether the unit itself is again built up by multiple processing or memory units, as long as the developer does not have to cater for it either – or more generally spoken, as long as the details are of no consequence for development.

The architecture thereby takes mainly a (software) developer's / optimiser's perspective – i.e. whilst it may not be suitable for the hardware developer, it provides a software developer aiming for high efficiency in his code execution with all essential information. Even though classical programming development neglects such aspects as latency to L1 cache, this information in combination with the size of this cache and the bandwidth of its connection proves vital for optimisation tasks and for identifying scalability issues. In heterogeneous environments, it furthermore provides the necessary data to identify the best distribution of dependent code segments. It may be noted in this context that hardware-specific adaptation steps are still necessary, even though subsumed in this model – for example, when two processing units have different ISAs.

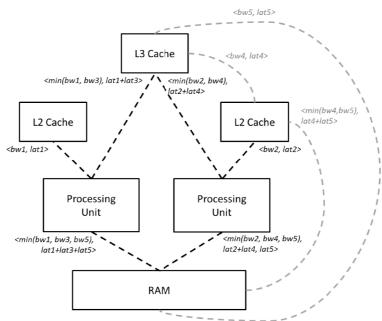

Figure 2: Flat description of a hardware architecture.

Even though S(o)OS does not try to address all these varieties in the same degree, the principles of S(o)OS can thus be extended to cover further architectures, such as cloud infrastructures, or even future processor architectures. With this architectural concept, it is possible to depict the whole layout of an infrastructure, down from the lowest processing units up to the highest-level systems. We can thereby choose between a flat or a hierarchical description of the infrastructure (cf. Figure 2). For more details about hardware descriptions, please refer to S(o)OS Deliverable 2.2 [31].

### 1.B) S(0)OS INFRASTRUCTURE CHARACTERISTICS

Though the new architectural structure allows for a wide variety of infrastructures to be covered, S(o)OS restricts itself to a selected subset of architectures in order to keep the effort feasible and improve the quality of the results. With S(o)OS aiming specifically at dealing with large-scale problems and improving their programmability, the primary application domain consists in high performance computing, as the according code has typically been explicitly developed for a high degree of scalability.

As S(o)OS deals with improving the parallel execution of code by exploiting inherent and explicit concurrency, it is relevant to estimate timing behaviour of code segments given specific conditions. A domain where the timing behaviour of software is actually critical is the one of real-time (RT) systems, where timing is at least as important as functional correctness. Furthermore, a notable class of RT applications exists where the high computational workloads can meet the in-place tight timing constraints only thanks to proper parallelisation and distribution techniques (we could think of these as belonging to a hybrid HPC-RT class). Accordingly, a secondary application domain for S(o)OS consists in time-sensitive applications – ranging from interactive to soft RT use cases. Both HPC and RT applications benefit from a highly predictable duration of code segments which should ideally be nearly constant, or with minimum variability. However, when this is not possible (as common in e.g., multimedia processing), HPC development cares particularly about the average-case performance for maximising the achievable throughput, whilst for RT development the focus is on the worst-case duration, or some percentile of its probabilistic distribution, for the purpose of respecting the in-place timing constraints, such as deadlines.

In particular S(o)OS thereby addresses the increasing need for interactive HPC use cases. Implicitly, the major infrastructure type consists in HPC and cluster machines that incorporate a high amount of resources with dedicated, high-performing interconnects. It is notable in these infrastructures, that their general hierarchy is comparatively flat, i.e. processors are connected as directly as possible (via I/O) without having multiple levels on top of them, such as servers, servers farms and world wide web (i.e., intranet and internet). Furthermore, even though HPC systems become more and more heterogeneous, their diversity is way lower than the heterogeneity in the Internet. In other words, HPC systems have a high degree of homogeneity, such as multiple GPU cards of the same type, multiple identical processors, etc. Similarly, the interconnect is typically very homogeneously arranged in order to maintain equal latency and bandwidth behaviour.

Further to this, it can be expected that the code already exhibits characteristics of parallelism and concurrency and that the algorithm is not essentially sequential in nature. The according programs typically also exhibit a minimum of OS interactions, thus making the dependencies clearer. As the major aim of HPC consists in execution performance, jobs are generally executed in an isolated fashion, both task and hardware wise. In other words, the OS does not need to handle multi-tasking aspects and generally does not have to cater for security. In all these cases, the according capabilities can be built up on this base model.

In general, the concepts of S(o)OS are by no means restricted to the given use cases – in fact it will be noted from the detailed descriptions below that the same principles can be applied to cater for other application domains, such as more general purpose home and office usage or distributed environments, such as clouds, or social networks. S(o)OS does not explicitly address them so as to not diverge from its main objectives (scalability and heterogeneity), by having to cater for additional concerns, such as security, task isolation, reliability etc.

#### A NOTE ON RELIABILITY

Since reliability is a major concern also for HPC applications, we must elaborate this latter issue in more detail: we can distinguish between different types of reliability, in particular between (a) reliable execution of the application and (b) reliability of the OS itself.

Reliable execution of type (a) refers to fault tolerance at runtime, i.e. that neither problems on the infrastructure or the application itself lead to an execution failure. This covers a vast research area in itself and can be mainly separated into the following main approaches: (1) execute the code in a managed framework, (2) replicate the application, i.e. execute it multiple times in parallel or (3) checkpoint the application in time and roll back when need be. Even though S(o)OS can be compared in parts with a managed framework, the according tasks (monitoring and adaptation) serve different purposes and are not executed everywhere. Similarly, replicating application execution is only sensible when the code size does not exceed a certain degree of scale, as otherwise this leads to bad resource utilisation in large scale environments such as envisaged by S(o)OS – more advanced algorithms try to identify the critical code segments, yet this is (for now) outside the scope of this project. Since S(o)OS aims to be general purpose, reliability would also have to cover dynamicity issues, which are generally unsolved as yet.

The most typical form of application level reliability in HPC environments consists in checkpointing at regular intervals and rolling back the application state if an unexpected error occurs. Notably, the same error may occur again if the code is buggy in itself. S(o)OS will indirectly support this approach by providing all essential means for checkpointing and rollback, yet either a middleware or the application itself will have to actually employ these capabilities according to the respective need of the use case.

As opposed to this, S(o)OS will address reliability on the level of the operating system itself, i.e. trying to ensure that the whole system does not fail with problems in a single node. This document does not explicitly address this issue though, as it will be subject to future work in the project.

#### 2. THE ROLE OF THE OS

The S(o)OS project proposes to address the problem of scalability and heterogeneity through a novel OS architecture approach which builds up from the lessons learned in Service-Oriented Architectures and Distributed Systems. All these domains are signified by a large degree of scalability, but at the same time by a comparatively low degree of communication and connectivity. As opposed to that, typical HPC scalable applications have a high demand of data exchange and thus require a strong interconnect. Naive programmers now implement a program in such a fashion that the degree of data exchange between threads is very high. What is worse, some parallel programs exhibit tendencies to act like a set of processes that require constant OS support – in these cases, OS communication strongly interferes with the interprocess communication, and OS execution stalls multiple processes at the same time.

From the application perspective, we can therefore distinguish different types of dependencies across threads, code segments and OS system functions that have different impact on the execution performance depending on their way of implementation. In general we can state that the "tighter" and more frequent a certain form of dependency (and implicitly communication) occurs, the higher the impact of any delay due to the implementation choices. For example, if the access to registers were delayed e.g. through a message-based access implementation, the code would hardly be executable any more. On the other hand, the impact of delaying a web service invocation even further is minimal from the total application execution perspective.

Due to the extended distribution features in S(o)OS which may involve separating an application at "arbitrary" points, the operating system needs to cater for different types of dependencies in

different forms of communication in a fashion that is mostly invisible to the application, and in particular to the developer – i.e. the developer should not have to cater for choosing the communication means for all different setups. For example current HPC developers have to consider the distribution of threads across cores and processors to implement a well-adjusted hybrid mix of OpenMP and MPI communications in order to achieve the best performance. Accordingly, the communication choices may fail in different infrastructures.

We can distinguish in particular the following levels:

- Register access: the lowest level of information access in a program and at the same time the

one with the highest frequency of occurrence. Register access is completely inherent to the

program code and generally not interceptable, nor is it sensible to increase the access delay. We

can generally assume that this level is unchanged.

- Memory access: in particular in shared memory applications, this level forms the most crucial

form of inter-process state and data sharing. Depending on the implementation choice and the

programming model used, this type of access is realised in completely different ways. Memory

access in general is very frequent in any form of application. The degree of memory sharing

depends very much on the type of application and its coupling.

- System calls & events: system calls are handled by the OS, leading to a non-negligible amount of cache swaps and to implicit communications on memory level. The amount of invocations is comparatively high, but lower than memory access.

- Remote procedure calls and inter process communication: the highest level of communication consists in explicit invocations of remote processes or services via dedicated messages. This type of communication is typically explicitly catered for in the code and delays are considered in the overall execution time.

Notably, there are further types of dependencies and communication on intermediary levels which however expose similar properties. What is of main importance here is that the highest levels are typically catered for by a middleware, whereas the lowest level is left up to the hardware. The intermediary levels are either completely neglected or left to the programmer (sometimes helped by the compiler), who faces a higher development effort and may (involuntarily) specialise the code for a specific infrastructure.

The S(o)OS approach tries to cater for all these levels in three major ways: (1) selecting, injecting and adjusting the communication according to the current deployment and distribution; (2) distributing code and threads according to their dependencies and hence communication requirements / restrictions; and (3) distributing and replicating operating system level support according to these dependencies.

# 3. MAIN S(0)OS PRINCIPLES

S(o)OS main concept builds on exploiting concurrency implicit and explicit to application code: as communication forms the major obstacle towards highly efficient and large-scaling code execution, the major task in parallelisation optimisation consists in reducing *any* communication between parallel processes / threads. Communication is encoded in the degree of dependencies between different parts of the code, thus including not only direct invocation and explicit messaging, but also common memory or data access and thus state sharing. Any two parts of the code can be considered "concurrent" to one another, if there is little to no dependency between these two. Ideally, the developer exploits this concurrency at development time and enables execution of a maximum number of independent threads in parallel. Typically however, dependencies cannot be avoided and a clever developer must attempt to reduce their impact to a minimum.

S(o)OS supports this task by analysing the code behaviour with particular respect to its cross-dependencies, i.e. potential points of concurrency. It will thereby not only consider low- or high-level communication dependencies, but in particular the intermediary dependencies with the operating system itself. It will thus not only support identification of the main segmentation points in the application itself, but even of the operating system itself.

The main principle of S(o)OS consists in splitting up the operating system into a series of essential functionalities that are atomic in nature, i.e. they should not further be subdivided, but provides the minimal set of capabilities whilst still maintaining maximum performance. It has been shown that [29] message-based communication between distributed kernels has a potential for avoiding performance bottlenecks of the OS when scaling to many-core architectures. By clever distribution and exploitation of concurrency, the messaging overhead can be massively reduced, thus improving the overall performance. This is supported at the same time by extending parallel execution beyond the point of "just" work / data distribution, to concurrent execution that no current programming model supports properly. This allows reducing the impact from Amdahl's law by even parallelising the sequential code part to a certain degree.

The essential OS functions therefore become "services" to the code (application or other OS segments). Similar to the principles of Service-Oriented Architectures, the individual services can be easily replaced with others, as long as they offer the same interfaces and the same functionalities. The service-oriented approach allows replacement of individual modules / services easily without affecting the whole OS. In other words, hardware specific adaptations, as well as application-specific services, can be realised easily by providing only the relevant modules in an adaptive fashion. This implies that the OS has to identify and deploy these modules though. The architectural concept of S(o)OS is described in more detail in section IV. 2.

In the following we will exemplify how an application behaves on such an OS.

#### 4. APPLICATION BEHAVIOUR

The lifecycle of a parallel and distributed application spans the whole range from development to actual execution on the destination platform. This covers in particular the following steps:

#### I. Development / Programming

Most applications are essentially sequential in nature, i.e. the underlying algorithm is not per se suited for a parallel, multi-core or multi-processor environment. Automatic parallelisation only reaches bad execution performance, so that in principle the developer has to think about parallelising the algorithm itself. Supporting tools for this are limited to low-level actions, rather than parallelisation of the overarching logic such as:

- parallel libraries that offer specific functions in a parallel fashion in particular mathematical libraries that provide functions e.g. for parallel matrix calculation;

- libraries or programming extensions to support communication or data exchange across threads (OpenMP, MPI, PGAS etc.).

In order to parallelise the application, the developer has to think about means to distribute the actual execution over the available cores, processors and nodes. This implies that he/she has to either split up the data and work among the processing units, and thereby has to respect the different communication modes in a heterogeneous environment.

#### II. Compilation

Even if the developer has parallelised the code and potentially optimised it for the destination platform, the compiler will still execute further parallelisation tasks and optimisation steps. When supporting languages or tools were used, the compilation step will replace the according commands with the respective parallel command pattern, such as replacing the OpenMP pragmas with the

according thread creation commands, or replacing the shared memory invocations with messaging in PGAS. Further to this, the compiler will perform specific optimisation steps dedicated to the respective hardware by identifying typical patterns and replacing them with the corresponding code patterns that suit the hardware best.

As a consequence of the compilation step, the resulting code is fixed to a specific platform, i.e. the executed optimisation and adaptation steps make the code most suited for the single selected infrastructure, but restricts its portability to platforms that are almost identical.

#### III. Submission and reservation

In HPC scenarios, the user submits the application execution to the job queue of the machine. As part of this, the developer will specify the required amount of nodes and time for execution of the code. Generally, it is currently not possible to specify more details, such as communication needs, quality restrictions or hardware needs. With the heterogeneity increasing, it slowly and more frequently becomes possible to specify the destination hardware, but generally it is assumed that the developer has put thoughts into this prior to selecting the machine.

The queues order the submissions on basis of their requirements and availabilities in the platform. In some cases, the queues will also respect priorities basing on customer type / role. The actual execution does not begin before the job queue has reached the according submission. Once the respective position in the queue is reached, the binary package is deployed.

#### IV. Deployment

Of the reserved resources, one instance is selected as the main node for execution. On this node, the actual job is deployed (stored) and invoked. Typically, the application itself is responsible for creating and deploying additional threads and to ensure their availability through unique identifiers.

In HPC scenarios, the nodes are reserved for the execution of a single application for the reserved time, and cannot be used for other purposes. In most cases, however, the resources are shared between multiple applications. In general, the hosting environment already needs to contain and run a middleware that enables deployment and communication (i.e. an operating system). In laaS environments, the user can deploy full environments that are typically hosted in the form of virtual machines.

#### V. Execution

The actual execution of parallel code is essentially identical to running multiple independent processes in a distributed environment, whereas each process (thread) is either explicitly invoked by the main thread or executed right after deployment. The differentiation between sequential and parallel code parts thereby poses the major problem for efficient code execution in large-scale environments (cf. Amdahl's law).

The main task for the middleware to realise parallel execution consists however in synchronisation and state maintenance across threads, as well as communication between them. This means that some level of the execution framework needs to be able to identify and distribute shared data – generally, rather than identifying specific data, the framework will distribute and maintain all data that is specified as "shared" in one way or another in the source code (s. e.g. PGAS). More low-level approaches require the user to explicitly send and synchronise all according variables. As a consequence, the communication overhead is typically high - and typically way higher than necessary.

#### VI. Profiling & Monitoring

During execution, the behaviour of an application is monitored with respect to resource usage, performance etc. so as to create a behaviour profile. Behaviour profiles give an indication of the software system requirements, including such aspects as memory size, computing and network

bandwidth requirements. Such information is helpful for the application developer to further improve the code performance, or to the run-time environment to adaptively schedule applications for maximum performance. Notably, this is very important for interactive and real-time applications (e.g., adaptive feedback-based scheduling). Profiling and monitoring information can also be used in order to react to faults or to adjust energy consumption.

Profiling information covers aspects such as:

- what is the duration and execution time of certain code segments, including the overheads due to scheduling, synchronisation and communications;

- what are the actual delays experienced as due to the communications among the distributed application components;

- what are the latencies experienced across various critical monitoring points of the application, including the end-to-end latency;

- what are the sustainable data throughput for various critical parts of an application execution, and where are the bottleneck.

Even though performance profiling, modelling and analysis are critical steps for real-time applications, they constitute sometimes important steps also in HPC scenarios. Indeed, often an HPC application needs to check whether the various parts of the computations carried out in a distributed fashion are exactly balanced (i.e., they exhibit similar execution times) or not, so it is important to keep under control the execution time of the various code segments.

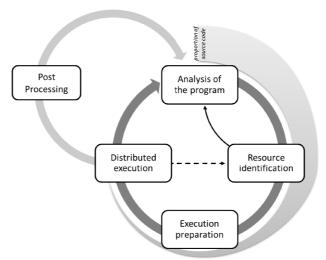

### 5. S(0)OS APPLICATION LIFE CYCLE

S(o)OS extends this application life cycle by explicitly adding means for the purpose of handling scalability and heterogeneity. In other words, by steps that are typically left up to the developer or the middleware into the operating system and adjusting the latter so as to cater for the implicit changes on the architecture.

Figure 3: S(o)OS' extended application lifecycle

Similar to the "classical" lifecycle, we can identify the following main phases:

- development/programming;

- compilation;

- code analysis;

- resource identification;

- execution preparation;

- execution;

post-processing.

Notably, as the operating system incorporates more dynamicity and adaptability than classical models, the phases become more interdependent. Execution may thus "jump" between phases, depending on the context triggers (cf. Figure 3). For example, profiling during execution may indicate that the application shows vectorial behaviour in parts, thereby enabling deployment on a vector processor — this automatically triggers redeployment of the code, given that the expected gain outweighs the cost for adaptation.

In the following sections we will explain these phases in more detail.

### 5.A) DEVELOPMENT

Program development in S(o)OS can be enriched with **high-level code annotations** that provide information about the dependencies of code executions (and hence principle concurrency) which could be exposed in the form of algorithmic descriptions ("code purpose", if you want); further annotations of that type could explicitly steer the behaviour of the S(o)OS components, such as specifying the best resource types for a specific task, which could support resource discovery in making a selection.

On the other hand, S(o)OS will expose **low-level code annotations** that are related to explicitly controlling the behaviour, such as dependency scope of an individual parameter, messaging specifics (send as block, send individually etc.), segmentation sizes etc. This will improve the performance of S(o)OS and hence the code execution, if the developer has enough knowledge about code behaviour and destination platform. Low-level annotations hence aim at expert (HPC) developers.

Similarly, real-time application developers will mainly benefit from a high-level declarative approach by which they will provide explicitly the timing constraints of their applications, in addition to the dependencies among code segments. The adaptive capabilities of the OS will manage to parallelise and deploy the application in a way that is suitable for meeting the in-place timing constraints. On the other hand, expert RT developers might prefer to use a lower-level control of scheduling and parallelisation, for improving predictability of a particular application execution on a particular hardware platform.

#### **5.B)** Compilation

Compilation in S(o)OS could be executed in different forms: since the OS (tools) will perform the final adaptation steps towards the destination platform, the code may not actually be converted into full machine code, but into an intermediary form. Also, due to the dynamic behaviour of the OS, the compilation should lead to an additional set of meta-information (such as dependencies) which could be used for analysis and deployment (and execution) purposes.

Accordingly, we can see at least the following options:

- **source-to-source**: the compiler converts the code into another code form that is closer to the actual S(o)OS specifics, e.g. C with low level annotations;

- source-to-intermediary: the compiler generates a "close-to-machine" code that can be easily

converted into machine code, but still contains relevant information about the last conversion

steps;

- **JiT compilation** (relates to source-2-intermediary): the actual compilation is executed on-the-fly, i.e. as soon as information about the destination platform and the code distribution is available;

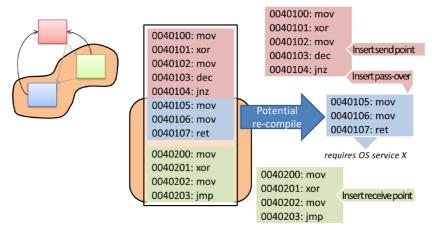

- **recompilation on the fly**: the compiler generates full machine code but provides enough information that allows detection of the appropriate source (or intermediary) code position to trigger recompilation if need be (see debugging symbols). In other words: during distribution, the OS detects that the destination platform differs from the existing compiled code version it

- therefore detects the according source code and requests the compiler to compile the according segment with different options (different destination);

- conversion on the fly: the most difficult way to treat heterogeneity consists in adapting the machine code on the fly to different platforms. This has no impact on the compiler - instead, compilation will be directed towards a generic platform, that allows easy adaptation to new systems. In general, this is not possible (e.g. different ISA) - however, low-level adaptations could be executed this way, depending on circumstances and purpose. For example, the same code can always be executed on a system with an extended (rather than a restricted) ISA; also, certain patterns can be identified to use these extended operations; adaptations such as data restructuring for a different cache organisation may also be possible etc.;

- multiple destination platforms: the compiler will create multiple branches of selected code areas with an additional annotation or branching mechanism to select the appropriate branch once the execution environment is known. Accordingly, non-executable or non-optimised code would take up memory space, but would not threaten execution, if the parameters can be read correctly. Some compilers already exploit these features in order to address a scope of (similar) platforms in the best fashion (e.g. Intel IPP2, Cray Compiler Environment). S(o)OS may use this information already during deployment to only select the appropriate branch.

Realistically, S(o)OS will take an approach that combines these options on different levels. Most likely seems the compilation to different destination platforms, whereby the individual destinations will be represented as generic and abstract as possible. The resulting code should have clear entry points for low-level adaptations, such as loop unrollment etc. through annotations during compilation process and according meta-information. These low-level adaptations are then executed on the fly, but only when necessary. Finally, when the destination deviates too much, or more complex adaptations are required, S(o)OS will trigger recompilation of the according segment.

It must be noted in this context that the choice of approach depends on multiple additional factors, the major one relating obviously to performance: not only should the approach realise efficient code that exploits the hardware features to its best, but the process itself should not conflict with the execution performance. Recompilation, adaptation etc. therefore should only be considered if the expected gain outweighs the cost for the according process – this, however, implies that the cost / benefit can be estimated beforehand. As this must base on the execution time of the respective code-segment, this requires a means to estimate the timing behaviour and compare it accordingly.

#### **5.c)** Code Analysis

The goal of code analysis consists in identifying potential points of parallelisation and, more importantly, the degree of concurrency implicit in the code. To this end, code analysis can take place on multiple levels:

- on source code: source code provides the level of concurrency as (intentionally or nonintentionally) provided by the developer. It furthermore provides the level of concurrency that is independent of the restricted memory architecture of the destination platform (i.e. registers instead of variables etc.) and is therefore on a higher level allowing for easier and more coarse segmentation. However, it does not contain any information about the actual code behaviour once fed with specific data (data-specific behaviour) and therefore cannot identify the size of parameter-bound loops;

- on machine code: the machine code level provides the low-level dependency information, including the memory related behaviour of the actual execution. On the one hand, this allows for more fine-grained and execution related segmentation. It also allows to watch the actual

D5.3 First OS Architecture (cc) BY-ND

24 | Page

<sup>&</sup>lt;sup>2</sup> http://software.intel.com/en-us/articles/intel-ipp/

data-specific behaviour. On the other hand, it provides too much detail and makes segmentation more difficult.

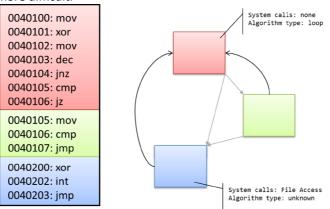

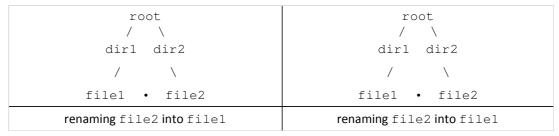

Figure 4: Basic blocks in an assembly code snippet and associated control graph.

The result of code analysis consists in a dependency graph. In the case of a highly scalable and mostly embarrassingly parallel application, this graph will be comparatively "sparse", e.g. you can identify loops that have high connectivity internally, but very little across iterations. Even though the source code based graph will look similar, the relation of amount of edges internal to and across the loops will be less clear (no count).

The resulting meta-information (graph and more) will enable a preliminary assessment with respect to the type of required resources (see next step).

#### 5.D) RESOURCE IDENTIFICATION

Once the code has been analysed regarding its main dependencies, the resulting graph can be analysed with respect to the specific hardware features that would suit the execution best. This involves aspects such as:

- big segment => large code heap

- data from external source => minimal cache hierarchy

- high interactivity => close to user

- data dependency => little latency

- small independent loops => vector

- etc.

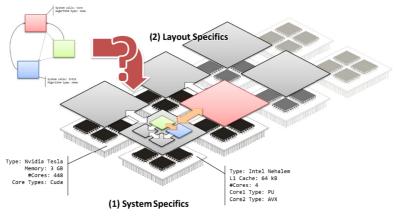

Figure 5: Layouting the code according to the infrastructure specifics

From this information, resource discovery is initiated, which tries to identify the most suitable resources fulfilling the requirements best. Notably, this does not mean that the code is restricted to

this type of resources (cf. compilation above), but that it will execute less efficiently in other environments.

For example in the case of a ray-tracing application, the best resources would be graphics cards with shader units (GPUs) and large memory. Since it is not clear from the analysis that this is a graphics related task, the actual request will look for vector units, rather than GPUs with at least 3 pipes but the more the better, and high memory capacity. Communication will be secondary, but still exist at some point with a single unit, thus preferring a star shaped layout. The resource specific information can be enhanced through profiling the application behaviour, as well as the resource performance given a specific code type (see execution and post-processing).

#### 5.E) EXECUTION PREPARATION

Prior to execution, the code will actually have to be adapted to the specifics of the destination platform - as already discussed in the development/programming step, this can take multiple forms. Within the context of this application, we can safely assume that a sufficient amount of graphics cards are actually available. Major point is rather to find the most suitable CPU for the execution of the main thread. We can furthermore assume that the developer knew that he/she was preparing a graphics related application and therefore specified GPUs as destination, which helps resource identification and code adaptation - this is not a general assumption though.

Figure 6:Different code segmentations and the impact on communication

If the code does not contain a GPU branch, it will have to be recompiled due to ISA compliance issues. However, only the individual render iterations need to be recompiled, whilst the rest is mainly CPU related and does not require recompilation.

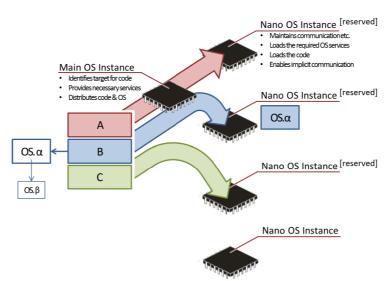

Once the destination resources are known, they will be reserved and prepared, i.e. all necessary OS modules for maintaining communication, loading code, executing rendering etc. will be loaded, along with the actual code. Notably, the actual code and the accompanying data will potentially only be uploaded at the time of spread-out. Further to this, all communication routes have to be established and set up. This follows the communication dependencies (i.e. data source and sink) as identified in the graph during code analysis. Here again, the communication is mostly star shaped, requiring mostly direct routes to the main thread.

Notably, in an ideal case the S(o)OS environment will also investigate at this point the different potential schedules for all code segments to achieve the highest throughput / resource utilisation. We can generally assume that there are less vector pipelines than pixels and hence loop iterations in our example. Accordingly, each unit will have to execute multiple iterations itself - either leading to multiple full loop iterations one after another, or to a single operation on a range of data, storing them individually. It is potentially possible that there are say 1.5 times more pixels than vector units, leading to half the resources being idle half of the time. If we leave timing (12 fps or similar) aside,

the free resources could be used to execute the next render iteration even after the sequential synchronisation part - potentially even purely speculative, if the interactions with the main thread are not fully known.

Figure 7: Deploying code segments in according resources

#### 5.F) DISTRIBUTED EXECUTION

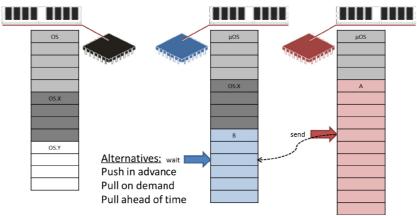

The actual execution involves off-loading code according to spread outs, initiating and maintaining communication, as well as ensuring state availability and consistency. Thereby, "threads" should be as minimal as possible and effectively just involve code deployment and execution.

Figure 8: Memory allocation of code segments, share data and OS services

Furthermore, during execution additional performance and dependency data may be gathered that may trigger re-analysis (step 1), if too many discrepancies are identified. Notably, rearranging the code has to be reassessed against potentially incurring costs.

In our example, the main thread will prepare the data for rendering (e.g. calculating some interactions or the camera position) and then spread out the actual rendering threads. Since there is no communication between the threads, but only with the main thread, the main data dependencies exist during spread-out and aggregation (synchronisation), where in both cases data is stored in the main thread. However, the individual renderers should not communicate all individual calculations back to the main thread, as this would lead to too much overhead.

Since ray-tracing are "static" applications, their behaviour does not change a lot during execution, i.e. no re-arrangement of code should be necessary.

#### 5.G) POST PROCESSING

In general, after execution the resources have to be freed for other processes again – this includes in particular freeing the memory, but in the case of distributed execution also the resource reservations have to be removed again, so as to make sure that the resources available for other processes. In addition, communication routes and configurations can be released again and the potentially deployed OS modules be removed, so that the resource can be discovered and initiated again (see section II. 5.d) ).

However, S(o)OS will allow for storing information about the monitored/observed code behaviour, so that it can be reused for future executions. The recorded monitored data includes code-specific information, such as dependencies and algorithm types, as well as hardware-specific information. Such information may be greatly useful for deploying the same application again in the future with a better performance.

The analysis results can be stored at multiple points in the execution process, but should at the latest be stored during post-processing. It may be noted in this context that code-related analysis results may also be stored as extended annotations in the source code, if the latter is accessible.

# III. USE CASES AND REQUIREMENTS

It has already been discussed in preceding sections how the concepts of S(o)OS aim towards supporting a generic hardware and software model. In other words, the concepts behind S(o)OS are designed so as to be generally independent of the underlying infrastructure and the type of application to be executed on top of it. This is due to the fact that S(o)OS principles behind identifying and addressing software requirements, respectively behind identifying and exploiting hardware capabilities are generally applicable to all currently known software and hardware models.

However, it must be noted in this context that not necessarily all applications actually expose characteristics that S(o)OS can exploit: some strongly sequential algorithms for example cannot efficiently be parallelised and distributed and thus will not benefit from S(o)OS specific support. S(o)OS specifically aims for supporting scalable application development and execution for and on large scale heterogeneous infrastructures. The project-related research and development will therefore specifically focus on scenarios and applications that can explicitly use the S(o)OS supporting features, thereby adding to the evaluation of the project success.

Accordingly, the most suitable use cases relate to applications with high-scale and specific time constraints, as detailed in what follows.

### 1. Specific Use Cases

Rather than considering the whole scope of the application scenarios as presented in D5.2 [15], S(o)OS will focus its efforts on use cases that can actually contribute to the S(o)OS objectives. In other words, that exhibit specific requirements towards hardware capabilities and expose behaviour characteristics that allow principally for segmentation and distribution.

With the overarching objectives of S(o)OS in mind (i.e. the capability to support large-scale heterogeneous environment), we can particularly identify two domains that specifically require support in the according directions and at the same time expose characteristics of relevance for S(o)OS:

- 1. **High Performance Computing**: HPC applications are generally explicitly written in a way that increases the level of concurrency, thus allows higher scalability with as little communication overhead as possible. HPC machines tend towards higher and higher heterogeneity, though at the same time, an according system typically offers a large number of each resource type.